### **ARITHMETIC CIRCUITS**

Arithmetic logic circuits are the logic circuits which perform arithmetic operations like addition, subtraction in digital computers.

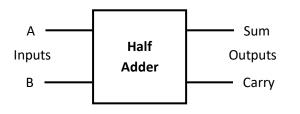

<u>Half adder:</u> It is a combinational logic circuit which performs the addition of two bits resulting in two outputs - Sum and Carry.

Block diagram of half adder

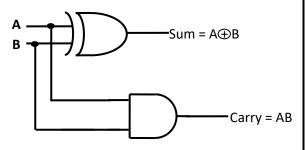

Logic diagram or logic circuit of half adder

## Truth table of half adder

| Inputs |   | Outputs   |            |  |

|--------|---|-----------|------------|--|

| А      | В | Sum = A⊕B | Carry = AB |  |

| 0      | 0 | 0         | 0          |  |

| 0      | 1 | 1         | 0          |  |

| 1      | 0 | 1         | 0          |  |

| 1      | 1 | 0         | 1          |  |

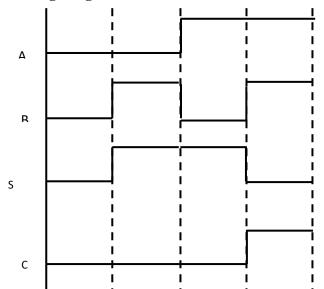

#### **Timing Diagram**

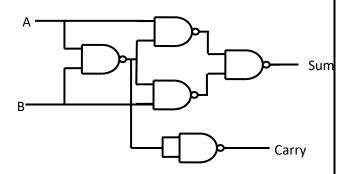

Half adder using universal NAND gates

**Boolean expression:**

$Sum = A \mathbf{\Phi} \mathbf{B} = \overline{\mathbf{A}} \mathbf{B} + \mathbf{A} \overline{\mathbf{B}}$  $Carry = \mathbf{A} \mathbf{B}$

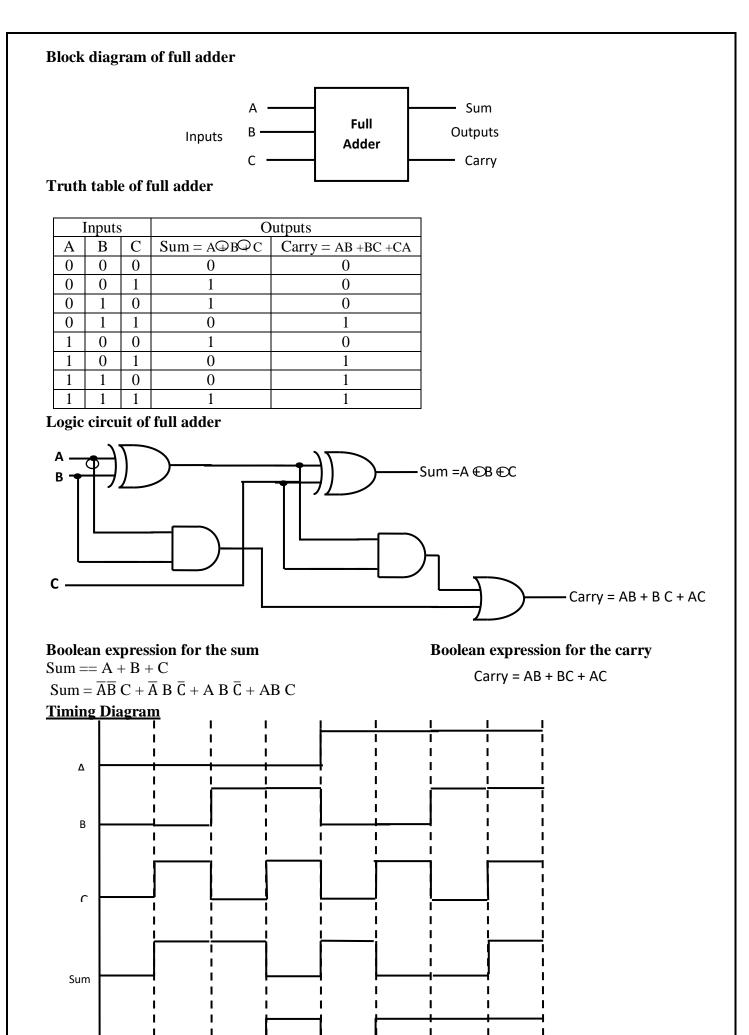

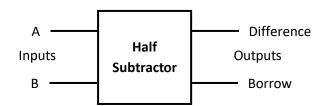

<u>Full adder:</u> It is a combinational logic circuit which performs the addition of three bits resulting in two outputs - Sum and Carry.

I

I

Т

L

I

Carry

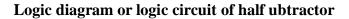

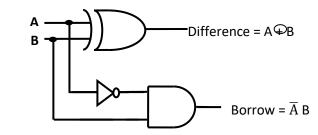

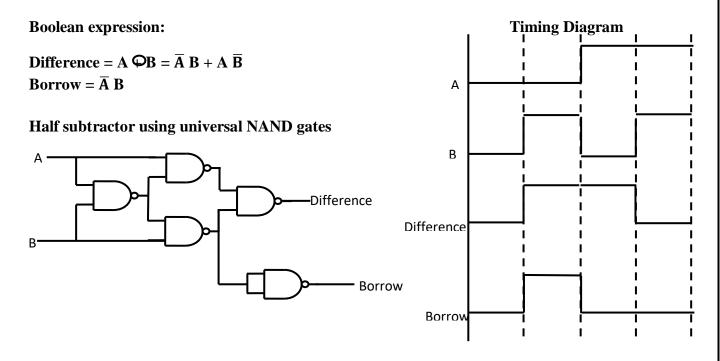

# Half Subtractor: It is combinational logic circuits which performs the subtraction of two bits resulting in two outputs - Difference and Borrow.

## **Block diagram of half Subtractor**

# Truth table of half Subtractor

| Inputs |   | Outputs          |                           |  |

|--------|---|------------------|---------------------------|--|

| А      | В | Difference = A⊕B | Borrow = $\overline{A}$ B |  |

| 0      | 0 | 0                | 0                         |  |

| 0      | 1 | 1                | 1                         |  |

| 1      | 0 | 1                | 0                         |  |

| 1      | 1 | 0                | 0                         |  |

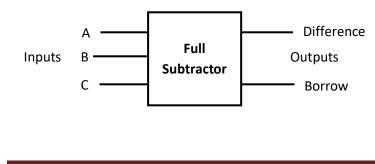

Full subtractor: It is combinational logic circuits which performs the subtraction of three bits resulting in two outputs difference and borrow.

## **Block diagram of full Subtractor**

#### Truth table of full subtractor

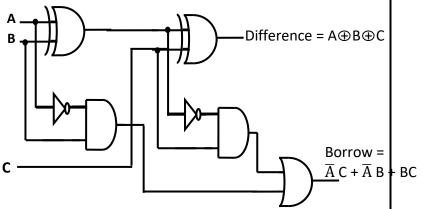

#### Logic circuit of full subtractor

|   | Input |   | Output                  |                           |        |

|---|-------|---|-------------------------|---------------------------|--------|

| Α | В     | C |                         | Borrow = $\overline{A} C$ | в 11 ) |

|   |       |   | $= A \Theta B \Theta C$ | $+ \overline{A} B + B C$  |        |

| 0 | 0     | 0 | 0                       | 0                         |        |

| 0 | 0     | 1 | 1                       | 1                         |        |

| 0 | 1     | 0 | 1                       | 1                         |        |

| 0 | 1     | 1 | 0                       | 1                         |        |

| 1 | 0     | 0 | 1                       | 0                         |        |

| 1 | 0     | 1 | 0                       | 0                         | c ———  |

| 1 | 1     | 0 | 0                       | 0                         |        |

| 1 | 1     | 1 | 1                       | 1                         |        |

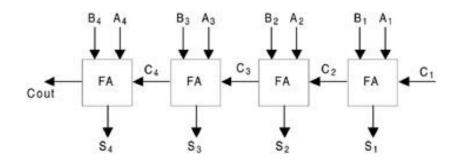

#### **4 BIT PARALLEL BINARY ADDER:**

A **Parallel Adder** is a digital circuit capable of finding the arithmetic **sum** of two binary numbers that is **greater than one bit** in length by operating on corresponding pairs of bits in parallel. It consists of **full adders connected in cascade** where the output carry from each full adder is connected to the carry input of the next higher order full adder

Consider two 4-bit binary numbers B  $_4$ B  $_3$ B  $_2$ B  $_1$  and A  $_4$ A  $_3$ A  $_2$ A  $_1$  are to be added with a carry input C  $_1$ . This can be done by cascading four full adder circuits as shown in Figure. The least significant bits A  $_1$ , B  $_1$ , and C  $_1$  are added to the produce sum output S  $_1$  and carry output C  $_2$ . Carry output C  $_2$  is then added to the next significant bits A  $_2$  and B  $_2$  producing sum output S  $_2$  and carry output C  $_3$ . C  $_3$  is then added to A  $_3$  and B  $_3$  and so on. Thus finally producing the four-bit sum output S  $_4$ S  $_3$ S  $_2$ S  $_1$  and final carry output Cout.

# **Magnitude Comparator**

Data comparison is needed in digital systems while performing arithmetic or logical operations. This comparison determines whether one number is greater than, equal, or less than the other number.

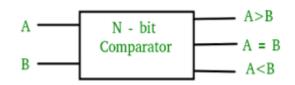

A Magnitude Comparator is a combinational circuit that **compares two binary numbers** in order to find out whether one binary number is equal, less than or greater than the other binary number.

The Block diagram of Magnitude Comparator is as shown below.

Types of Magnitude Comparator:

- 1. 1-bit magnitude comparator.

- 2. 2-bit magnitude comparator.

- 3. 3-bit magnitude comparator.

- 4. 4-bit magnitude comparator.

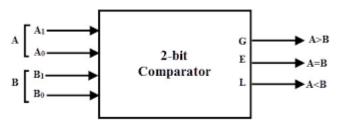

# 2-bit magnitude comparator:

A 2-bit comparator compares two binary numbers, each of two bits and produces their relation such as one number is equal or greater than or less than the other. The figure below shows the block diagram of a two-bit comparator which has four inputs and three outputs.

The first number A is designated as A = A1A0 and the second number is designated as B = B1B0. This comparator produces three outputs as G (G = 1 if A>B), E (E = 1, if A = B) and L (L = 1 if A<B).

The truth table for a 2-bit comparator is given below:

|                | Inputs           |    |                | Outputs |     |                   |

|----------------|------------------|----|----------------|---------|-----|-------------------|

| A <sub>1</sub> | $\mathbf{A}_{0}$ | B1 | B <sub>0</sub> | A>B     | A=B | A <b< th=""></b<> |

| 0              | 0                | 0  | 0              | 0       | 1   | 0                 |

| 0              | 0                | 0  | 1              | 0       | 0   | 1                 |

| 0              | 0                | 1  | 0              | 0       | 0   | 1                 |

| 0              | 0                | 1  | 1              | 0       | 0   | 1                 |

| 0              | 1                | 0  | 0              | 1       | 0   | 0                 |

| 0              | 1                | 0  | 1              | 0       | 1   | 0                 |

| 0              | 1                | 1  | 0              | 0       | 0   | 1                 |

| 0              | 1                | 1  | 1              | 0       | 0   | 1                 |

| 1              | 0                | 0  | 0              | 1       | 0   | 0                 |

| 1              | 0                | 0  | 1              | 1       | 0   | 0                 |

| 1              | 0                | 1  | 0              | 0       | 1   | 0                 |

| 1              | 0                | 1  | 1              | 0       | 0   | 1                 |

| 1              | 1                | 0  | 0              | 1       | 0   | 0                 |

| 1              | 1                | 0  | 1              | 1       | 0   | 0                 |

| 1              | 1                | 1  | 0              | 1       | 0   | 0                 |

| 1              | 1                | 1  | 1              | 0       | 1   | 0                 |

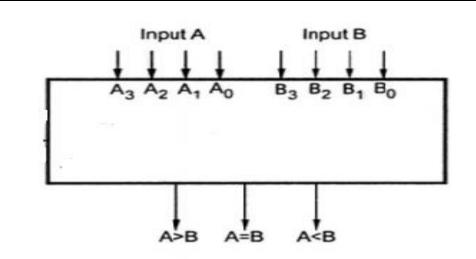

# **4-Bit Comparator**

It can be used to compare two four-bit words. The two 4-bit numbers are  $A = A_3 A_2 A_1 A_0$ and  $B_3 B_2 B_1 B_0$  where  $A_3$  and  $B_3$  are the most significant bits.

It compares each of these bits in one number with bits in that of other number and produces one of the following outputs as A = B, A < B and A > B.

The output logic statements of this converter are

- If A3 = 1 and B3 = 0, then A is greater than B (A>B). Or

- If A3 and B3 are equal, and if A2 = 1 and B2 = 0, then A > B. Or

- If A3 and B3 are equal & A2 and B2 are equal, and if A1 = 1, and B1 = 0, then A>B. Or

- If A3 and B3 are equal, A2 and B2 are equal and A1 and B1 are equal, and if A0 = 1 and B0 = 0, then A > B.

## **Block diagram:**

# Truth table

| COMPARING INPUTS                                               |         |         | OUTPUT  |       |       |                           |

|----------------------------------------------------------------|---------|---------|---------|-------|-------|---------------------------|

| A3, B3                                                         | A2, B2  | A1, B1  | A0, B0  | A > B | A < B | $\mathbf{A} = \mathbf{B}$ |

| A3 > B3                                                        | Х       | Х       | Х       | Н     | L     | L                         |

| A3 < B3                                                        | Х       | Х       | Х       | L     | Н     | L                         |

| A3 = B3                                                        | A2 >B2  | Х       | Х       | Н     | L     | L                         |

| A3 = B3                                                        | A2 < B2 | Х       | Х       | L     | Н     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 > B1 | Х       | Н     | L     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 < B1 | Х       | L     | Н     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 = B1 | A0 > B0 | Н     | L     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 = B1 | A0 < B0 | L     | Н     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 = B1 | A0 = B0 | Н     | L     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 = B1 | A0 = B0 | L     | Н     | L                         |

| A3 = B3                                                        | A2 = B2 | A1 = B1 | A0 = B0 | L     | L     | Н                         |

| H = High Voltage Level, L = Low Voltage, Level, X = Don't Care |         |         |         |       |       |                           |

## **Reference Books:**

- 1. Thomas L. Floyd, "Digital Fundamentals," 11th Edition, Pearson Education, 2015.

- A.P. Malvino, D. P. Leach, and Saha, "Digital Principles and Applications," 8th Edition, TMH, 2014.

- 3. https://www.electronics-tutorials.ws/combination/comb\_8.html

- 4. https://www.elprocus.com/digital-comparator-and-magnitude-comparator/